台灣半導體製造業位居全球重要地位,也是台灣重要的產業發展項目,隨著技術演進,元件尺寸越來越小、結構越來越複雜,傳統薄膜製程技術 (PVD, CVD) 漸漸無法滿足這些需求。原子層沈積技術藉由表面一層一層成長的獨特機制,具有高度均勻性、精準厚度控制、高階梯覆蓋率等特性,克服傳統製程技術所遭遇的困難。

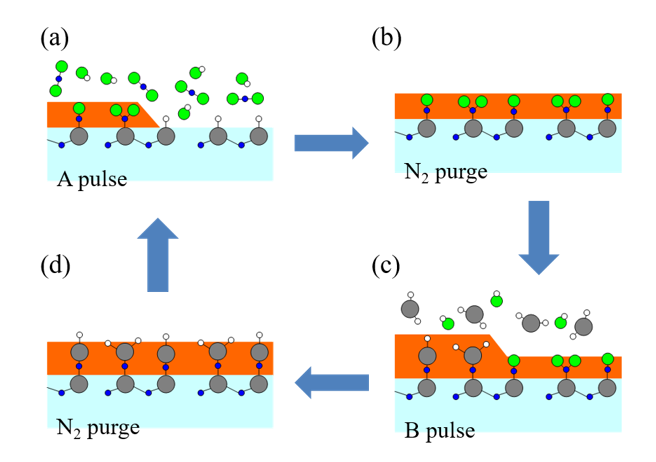

圖一、成長材料AB的ALD製程循環。

圖一、成長材料AB的ALD製程循環。什麼是原子層沈積?

原子層沈積 (Atomic Layer Deposition, ALD) 是一種可以將材料一層一層成長的薄膜製程技術,一般常見的ALD製程由四個步驟組成,以成長材料AB為例(圖一),(a)首先將含有A成分的化學氣體與基板反應,(b)利用大量惰性氣體(例如氮氣、氬氣)將化學氣體移除,(c)投入含B成分的化學氣體進行反應,(d)再次注入大量惰性氣體將剩餘的化學氣體移除,然後重複步驟a。藉由這四個步驟,含有A成分與B成分的化學氣體在整個製程過程中不會相互接觸,因此所有反應只會發生在基板表面,每一次循環的過程僅形成厚度為一層原子的薄膜,也因此讓每次鍍膜厚度的精確性達原子級(約0.1 nm)的尺度,並具有極佳均勻性。也因為成長過程被侷限在基板表面,在具有結構的表面上也能得到很好的覆蓋率與均勻性。

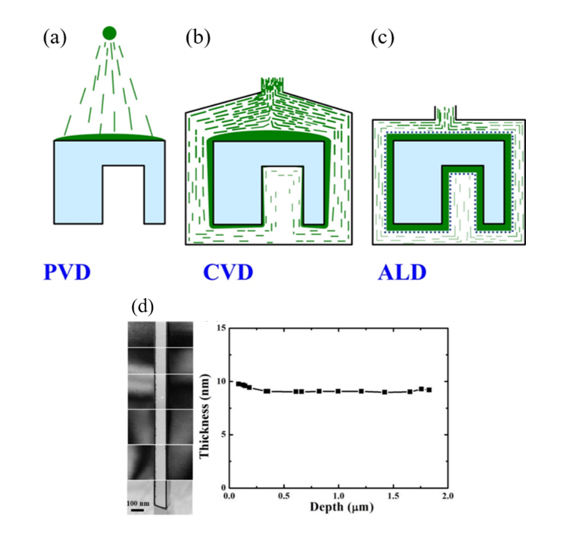

圖二、3D薄膜成長機制比較:(a) PVD與 (b) CVD均受限於材料源頭與目標的相對位置限制,無法達成均勻鍍膜,(c)ALD藉由獨特的表面成長機制,可以不受結構限制長均勻薄膜。(d)用ALD在開口為100 nm、深度18 μm的溝槽結構成長厚度為8 nm的薄膜,各個位置厚度誤差小於1 nm。

圖二、3D薄膜成長機制比較:(a) PVD與 (b) CVD均受限於材料源頭與目標的相對位置限制,無法達成均勻鍍膜,(c)ALD藉由獨特的表面成長機制,可以不受結構限制長均勻薄膜。(d)用ALD在開口為100 nm、深度18 μm的溝槽結構成長厚度為8 nm的薄膜,各個位置厚度誤差小於1 nm。3D薄膜製程挑戰

ALD藉由將材料一層一層成長在基板表面,雖然在成長速度上比傳統的物理氣相沈積(Physical Vapor Deposition, PVD)與化學氣相沈積(Chemical Vapor Deposition, CVD)薄膜製程緩慢,但因ALD獨特的表面成長機制,使其不受表面結構影響,可以形成厚度均勻的薄膜(圖二),同時因每一次循環僅形成為一個原子層厚度的薄膜,可以達到極為精準的膜厚控制。且ALD所需要的製程溫度遠低於PVD及CVD,可以應用在一些無法承受高溫的基板材料。當元件發展逐步朝向尺寸微小化,結構複雜化的方向演進時,ALD將逐步取代傳統PVD、CVD製程。

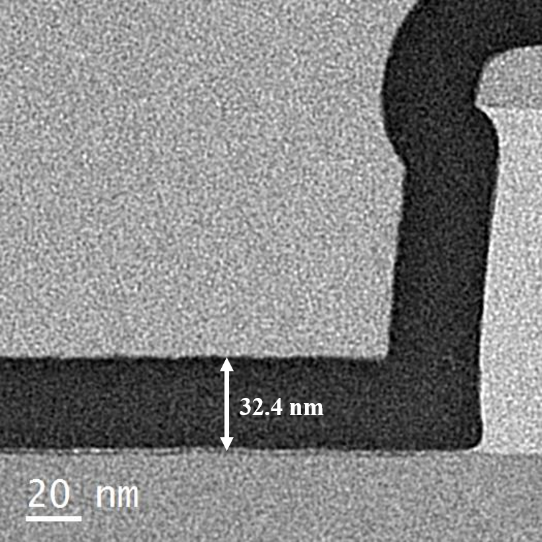

圖三、在具有結構的鰭狀電晶體外壁以 ALD 技術成長厚度均勻的薄膜。

圖三、在具有結構的鰭狀電晶體外壁以 ALD 技術成長厚度均勻的薄膜。原子層沈積技術的應用

ALD技術具有極佳的薄膜成長厚度控制性、階梯覆蓋性與大面積均勻性,此具有極高的應用價值,例如在元件越做越小的半導體產業中,ALD 已逐步取代傳統鍍膜製程。例如在鰭狀電晶體 (FinFET) 外側鍍製厚度均勻的介電層(dielectric) (圖三)。此外、在能源開發領域 ALD 可以製作極薄的保護層,提升鋰電池的使用壽命,或者改變介面性質提升電子傳輸效率,提升太陽能電池整體效能。在生醫、催化領域也有應用 ALD 技術的相關報導,可想而知隨著科技持續發展,未來將會發現越來越多的 ALD 應用。