在矽晶片上製作元件,就像是在現今的都會區蓋集合式住宅,盡可能的達到土地利用的最大化。在奈米的世界裡,矽晶圓上製造堆疊元件的晶片,必須在一定的單位面積中做最高價值的應用,進而衍生從傳統平面結構電晶體發展到三維堆疊,不但要縮減元件占用面積還需增加運作效能。

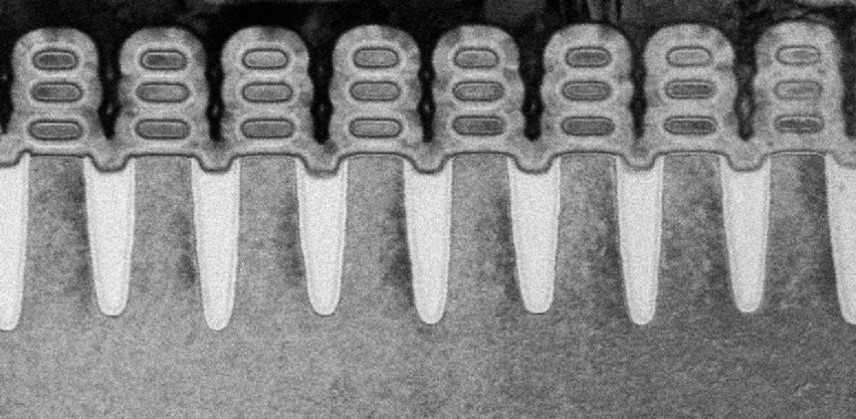

堆疊的環繞式奈米片

(圖片出處:IBM https://spectrum.ieee.org)

一直以來,半導體技術隨著摩爾定律不斷微縮,從微米等級的傳統平面式電晶體,到奈米等級開始使用的鰭式電晶體(22nm),都將無法滿足摩爾定律對元件的持續要求,為了應對未來小於2nm技術結點所面臨的挑戰,利用水平堆疊的環繞式奈米線/奈米片。可以在與鰭式電晶體的製程差異最小的情況下進行製造[1]。

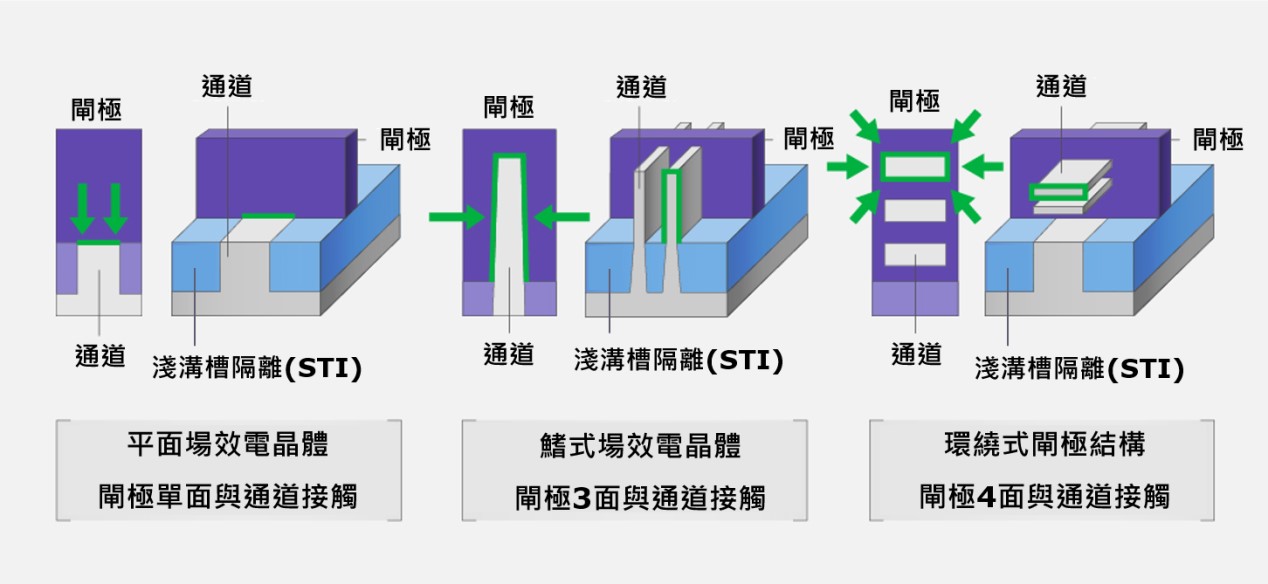

(圖片出處:Samsung https://news.samsung.com)

以傳統電晶體而言,在同一接觸面上(綠線)分為控制電壓的金屬閘極(上方)與感受電壓的半導體(下方)作為電子傳遞通道。而鰭式電晶體利用凸出的三維結構,增加了兩個側壁平面與閘極的接觸面積,進而改善閘極對通道電場的控制能力,然而經過近幾年來的持續發展與製程的進步,鰭式電晶體仍無法滿足業界微縮尺寸的需求。為了突破鰭式電晶體三維空間的限制,發展出環繞式電晶體結構,四面皆是閘極與通道的接觸面,閘極控制面積的最大化全方位的包覆通道來有效控制電壓。

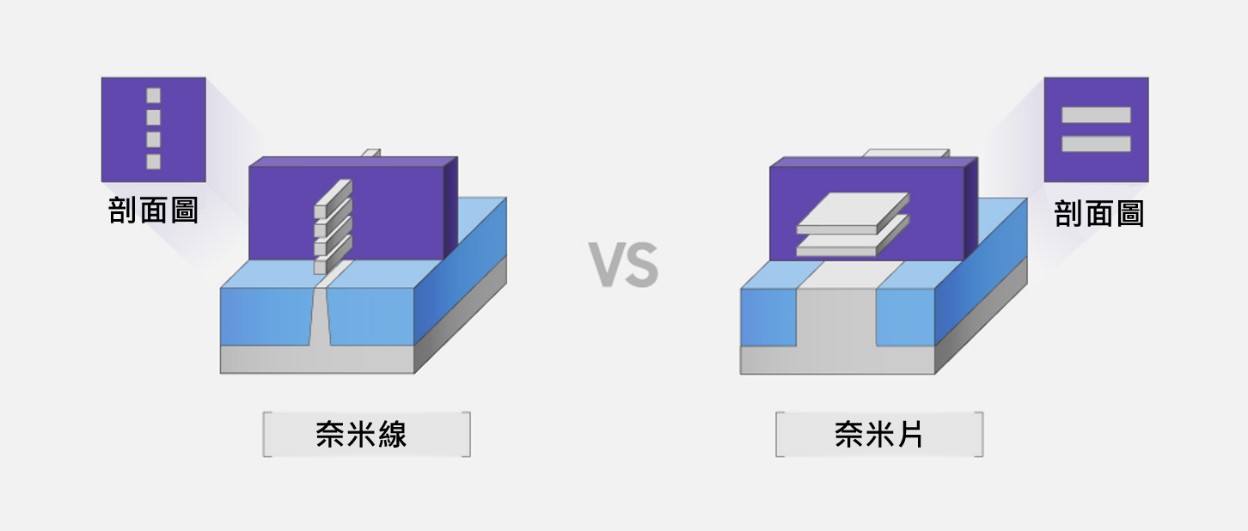

(圖片出處:Samsung https://news.samsung.com)

在環繞式電晶體中又分為兩種,奈米線與奈米片[2]。奈米線利用鰭式電晶體的結構,經由選擇性蝕刻製程移除部分結構,再包覆閘極金屬可做到,但電子通道的截面積(剖面圖) 仍無法取代鰭式結構的通道截面積,導致電阻過高大電流不易通過。因此發展出堆疊式的多層奈米片,才有足夠的截面積取代鰭式電晶體容納高電流通過,與現有7奈米鰭式電晶體相比,堆疊式的奈米片佔用面積減少45% ,同時性能提升30%與功耗節省50% ,在目前的市場上是極具競爭力的電晶體結構。

[1] N.Loubet et al., “Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET,” in 2017 Symposium on VLSI Technology, 2017, vol. 5, no. 1, pp. T230–T231.

[2] J.Zhang et al., “High-k metal gate fundamental learning and multi-Vt options for stacked nanosheet gate-all-around transistor,” in 2017 IEEE International Electron Devices Meeting (IEDM), 2017, vol. 56, no. 6, pp. 22.1.1-22.1.4.