利用原子層沉積技術在深寬比達 9:1 奈米球結構上製作高覆蓋性氧化鋁奈米球殼

利用原子層沉積技術在深寬比達 9:1 奈米球結構上製作高覆蓋性氧化鋁奈米球殼隨著半導體元件微小化,現行的製程技術與材料皆面臨極大的挑戰,例如 2006 年 Inteational Technology Roadmap for Semiconductors ITRS 預估在 2013 年半導體製程切入 32 奈米節點時,動態隨機存取記憶體 (DRAM) 中溝槽式電容結構的深寬比將達到 100:1,溝槽寬度 60 nm 僅為人體最微細血管的二百分之一,該結構製程必須在溝槽內均勻地沉積厚度 1 nm 的電容層,此 1 nm 的厚度僅為人體 DNA 直徑的一半。目前已知未來半導體技術將朝向大面積、日趨縮減的奈米級線寬、更薄的介電薄膜及更嚴苛的厚度均勻性等方向演進,這些技術門檻無疑對現有薄膜製程是非常大的挑戰,因此相關產學研各界對奈米結構原子級薄膜製程設備的需求極為殷切。

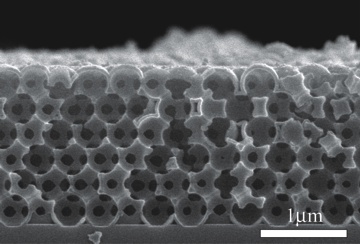

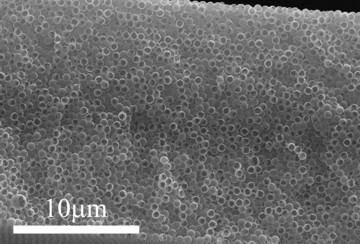

利用原子層沉積技術在深寬比達 60:1 奈米球結構上製作高覆蓋性氧化鋁奈米球殼

利用原子層沉積技術在深寬比達 60:1 奈米球結構上製作高覆蓋性氧化鋁奈米球殼傳統上,半導體廠是以物理氣相沉積 (Physical Vapor Deposition, PVD) 鍍膜或化學氣相沉積 (Chemical Vapor Deposition, CVD) 鍍膜,在溝槽結構上製作電容層,但是當溝槽深寬比達 7:1 時,PVD 與 CVD 兩種方法在溝槽開口處沉積電容物質較快,而溝槽底部較慢,導致溝槽底部的階梯覆蓋率 (step coverage) 不佳而造成元件失效。當國際大廠想盡辦法解決階梯覆蓋率不佳的問題時,發現原子層沉積法可在高深寬比溝槽上,製作階梯覆蓋率極佳的薄膜。原子層沈積 (Atomic Layer Deposition, ALD) 技術乃利用製程氣體與材料表面進行化學吸附反應,因此種反應具有「自我侷限」(self-limited) 特性,使得每一次進氣循環的過程,僅形成厚度為一層原子的薄膜,此項特性讓控制鍍膜厚度的精確性可達原子級 (約十分之一奈米) 的尺度;相較於傳統薄膜製程,ALD 技術形成的薄膜,其成長過程被侷限在材料表面,使薄膜具高階梯覆蓋率及極佳的厚度均勻性。

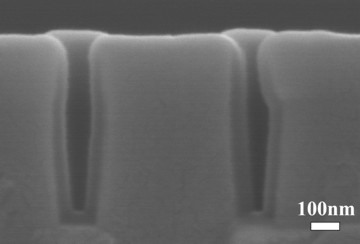

利用原子層沉積技術在深寬比達 6:1 溝槽結構上製作高覆蓋性氧化鋁薄膜

利用原子層沉積技術在深寬比達 6:1 溝槽結構上製作高覆蓋性氧化鋁薄膜一般而言,奈米科技研發方式分為:(1)由下而上 (Bottom→up) (2) 由上而下 (Top→down) 兩類。此次發表的「原子層沉積 (ALD) 鍍膜系統」,為一由下而上 (Bottom→up) 的奈米製程技術,它是藉著控制反應氣體無所不至的特性,以漸近無中生有的過程,來達到所需要的膜厚尺寸。原子層沉積技術同時具有大面積、高階梯覆蓋率、高厚度均勻性、低溫製程及原子級膜厚控制等優點,除了可以有效解決超薄高介電材料鍍膜需求外,亦可應用於半導體奈米製程技術之銅擴散阻絕層,如:氮化鉭阻障層 (TaN barrier layer) 及沉積鎢金屬,另亦可針對微小的電路結構,提供很好的孔洞填補能力。同時可用於複雜的 DRAM 電容結構與微機電元件等技術所需的高深寬比均勻鍍膜製程。目前國際半導體設備大廠如 Applied Material、Axitron-Genus 與 ASML 等,皆已致力於 ALD 量產機台設備的研發與推廣,依據 VLSI Research 統計,全球原子層沈積系統 (ALD) 銷售金額已由 2003 年約一億美金,快速增加到 2006 年的四億美金,預計至 2015 年可達 30 億美金規模。

利用原子層沉積技術在深寬比達 6:1 溝槽結構上製作高覆蓋性氧化鋁薄膜

利用原子層沉積技術在深寬比達 6:1 溝槽結構上製作高覆蓋性氧化鋁薄膜我國半導體產業發展快速,已創下高達兆元的產值,各大廠對製程設備之投資更是不遺餘力,不過這些昂貴的設備幾乎完全仰賴國外進口,關鍵製程技術也多來自於外國廠商的支援,使得國內半導體業主要訂單多為代工,耗費大量資源來賺取微薄利潤,因此產官學各界尋求半導體製程設備自主化及技術本土化可行性之努力從未間斷。為了解決半導體產業在元件製程上的瓶頸與降低對進口設備的過度依賴,國家實驗研究院儀器科技研究中心 (儀科中心),成功開發一套由國人自行設計研發的 ALD 系統,並經高介電材料製程驗證,可於低溫、粗略真空環境下,進行高階梯覆蓋率 (100%)、高厚度均勻性 (< 1% 厚度變化,4 inch 晶圓) 及原子級薄膜厚度控制成長 (0.1 nm)。在階梯覆蓋率與膜厚均勻性兩項特性上均已達國際水準,薄膜成長速率 (30–50 nm/hr) 亦符合業界要求。該技術除了滿足半導體產業於元件製程研發階段的需求外,同時可提供學術界進行奈米結構材料製程與特性的研究,具有潛力發展成為量產型研究機台,與目前進口動輒新台幣二千萬元起跳研發型機台相比較,儀科中心開發性能相近的系統價格僅約進口設備的 1/3–1/2,在性能與價格上,皆是一極具競爭力的鍍膜系統。此項技術開發過程中儀科中心更與交大前校長張俊彥教授團隊及清大材料系教授現元智大學彭宗平校長研究團隊等學術單位進行前瞻技術開發,而研究成果已於奈米領域知名期刊 Nano Letter (Impact Factor 9.96) 中發表,未來將繼續與各界共同合作開發,以提升台灣在次世代半導體產業領先地位。此次發表的 ALD 系統即以一次只成長一層原子 (約 0.1 nm 厚) 的方式,於基材上形成均勻薄膜,由於奈米級高深寬比溝槽結構限於廠商機密取得不易,儀科中心利用溶液沉澱堆疊方法,製作出多層堆疊的奈米塑膠球結構,驗證 ALD 鍍膜技術可在深寬比達 60:1 的結構上製作階梯覆蓋率高且均勻的薄膜 (如所附照片),此結果充分展現本系統具備未來應用於 32 奈米世代的 IC 製程中所需的製程能力。本次發表之技術為該中心累積多年來在真空科技領域所建立的卓越基礎,自行開發完成的原子層沉積鍍膜系統,可利用此系統提供學術界發展原子級高介電薄膜等相關製程研究與設備技術。

4 吋基板原子層沉積系統

4 吋基板原子層沉積系統儀科中心目前已完成適用於 4 吋與 8 吋晶圓的 ALD 鍍膜系統開發,並獲得國科會(103年3月改制為科技部)工程處的肯定,於 97 年度提供經費支持,建立適用於 12 吋晶圓的 ALD 鍍膜系統,除了挑戰大面積與高深寬比結構鍍膜研究,也將技術能量延伸至 32 nm 所需金屬閘極與擴散阻絕層等關鍵製程,同時進行試量產之研究,目前已有本土真空製程設備廠商表達技轉意願,並希望建立研發型的量產機台,同時也已接獲國內外研發單位的探詢。藉由此項技轉過程,將可提供國內產學界性能與價格上皆具競爭力的 ALD 系統,使 ALD 技術在國內開花結果。對於我國發展下世代半導體前段製程設備所需完整技術能力的建立,將具有重要的實質貢獻。儀科中心約三十年前即投入真空技術研究發展,由真空元件製造著手,將技術移轉予業界生產銷售,並首先將真空極限推至 10−10 Torr 超高真空領域,成為國內真空技術的研究重鎮。目前研究重點為太空級規格光學薄膜元件與奈米薄膜材料之製程與設備開發,在服務績效的提昇方面,則持有 TAF (全國認證基金會) 校正領域認可證書,長期提供各界具有公信力之壓力校正服務。為協助相關產業提升技術,該中心近年來先後發表「奈米製程微流量校正系統」及「半導體電漿製程漏氣微型光譜即時偵測器」等二項真空技術研發成果;亦為清華、中正、台大等學術單位與大同公司等產業界,提供薄膜製程所需之真空系統設計、製作與維護等技術服務。